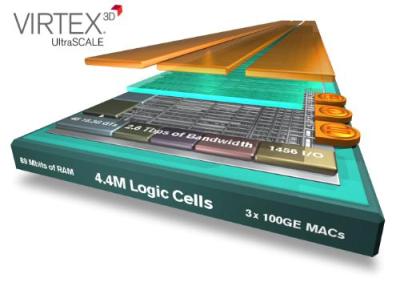

Xilinx (Irlanda) ha annunciato oggi un nuovo dispositivo che segna il record di 4,4 M di celle logiche, più del doppio della capienza del preesistente Virtex®-7 2000T (già in testa alla classifica del settore), ottenendo così la leadership in due generazioni consecutive di dispositivi e offrendo ai clienti un vantaggio equivalente a un ulteriore nodo tecnologico. Quale membro di punta della famiglia All Programmable UltraScale™ di Xilinx, anch'essa annunciata oggi, il circuito integrato tridimensionale Virtex® UltraScale™ VU440 rafforza la leadership di Xilinx portandola da un fattore 2 per i 28 nm a un fattore 4 per i 20 nm - e offrendo una capienza maggiore rispetto a qualunque altro dispositivo programmabile.

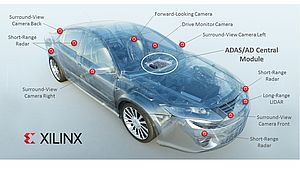

Grazie a un'avanzata tecnologia tridimensionale, il dispositivo VU440 con processo a 20 nm fornisce prestazioni maggiori rispetto a quanto preannunciato pubblicamente dalla concorrenza per il processo a 14/16 nm. Il dispositivo Virtex UltraScale VU440 fissa un nuovo parametro di riferimento per il settore fornendo 50 M di porte ASIC equivalenti, ideali per le applicazioni di produzione e prototipazione della prossima generazione. I chip Virtex UltraScale a 20 nm offrono inoltre le più alte prestazioni di sistema e la maggiore larghezza di banda nelle implementazioni a singolo chip di applicazioni quali MuxSAR 400G, transponder 400G e ponti MAC-to-Interlaken 400G.

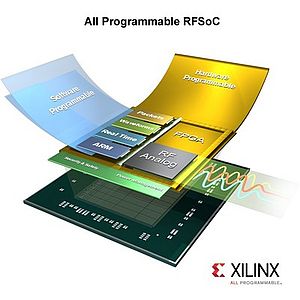

Fondamentale per la larghezza di banda e per la capienza del dispositivo, che si collocano ai vertici del settore, è la tecnologia Stacked Silicon Interconnect (SSI) di seconda generazione. Basata sulla tecnologia di fabbricazione CoWoS di TSMC, questa nuova generazione della tecnologia SSI si caratterizza per una larghezza di banda tra i die quintuplicata e per un'architettura di clock unificata ai confini tra le slice, che consentono un'esperienza di progettazione analoga a quella di un dispositivo monolitico. La tecnologia SSI consente a Xilinx di realizzare dispositivi con una capienza doppia o quadrupla rispetto ai prodotti concorrenti, mantenendo un vantaggio rispetto ai progressi possibili in virtù della sola legge di Moore.

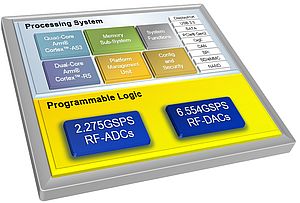

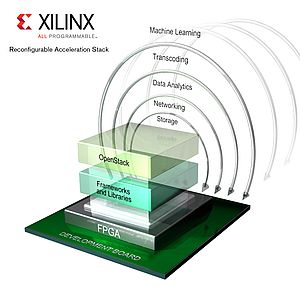

Xilinx ha inaugurato la propria tecnologia SSI con il Virtex-7 2000T nel 2011 - all'epoca il dispositivo più capiente al mondo- contenente 6,8 miliardi di transistor, offrendo ai clienti la possibilità di utilizzare 2 M di celle logiche, un numero senza precedenti equivalente a 20 M di porte ASIC. I dispositivi UltraScale di Xilinx offrono vantaggi analoghi agli ASIC poiché impiegano l'unica architettura programmabile 'di classe ASIC' oggi disponibile, applicabile alla tecnologia planare a 20 nm così come alla tecnologia FinFET a 16 nm, agli IC monolitici e agli IC tridimensionali. Grazie alla combinazione tra l'avanzata tecnologia di TSMC (co-ottimizzata con la suite di progettazione Vivado, di livello ASIC) e la metodologia di progetto UltraFast™ recentemente presentata, Xilinx ha compiuto con un vantaggio di uno o due anni un nuovo balzo - di un fattore 1,5 o 2 - nelle prestazioni e nell'integrazione realizzabili a livello di sistema. Disponibilità I dispositivi Xilinx® UltraScale™ sono supportati nella versione 2013.4 della suite di progettazione Vivado®. La completa documentazione di prodotto è già disponibile alla pagina www.xilinx.com/virtex-ultrascale.

Per sapere di più sull'architettura UltraScale, visitare www.xilinx.com/ultrascale. La consegna dei dispositivi Virtex UltraScale avrà inizio nella prima metà del 2014.